什么是沉积工艺?

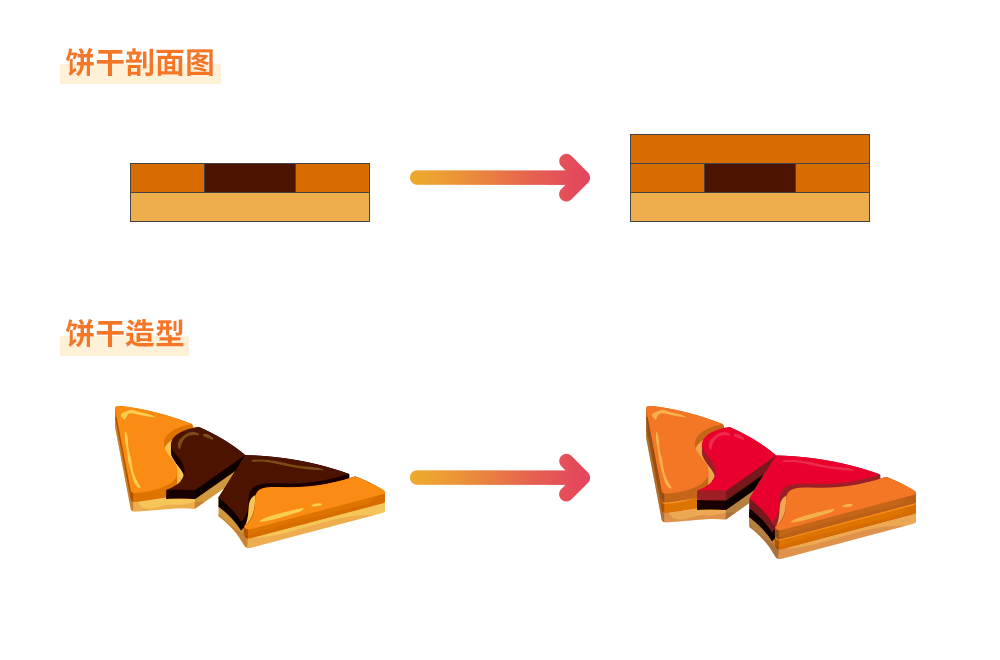

为制作巧克力夹心,需通过“刻蚀工艺”挖出饼干的中间部分,然后倒入巧克力糖浆,再盖上一层饼干层。“倒入巧克力糖浆”和“盖上饼干层”的过程在半导体制程中就相当于“沉积工艺”。

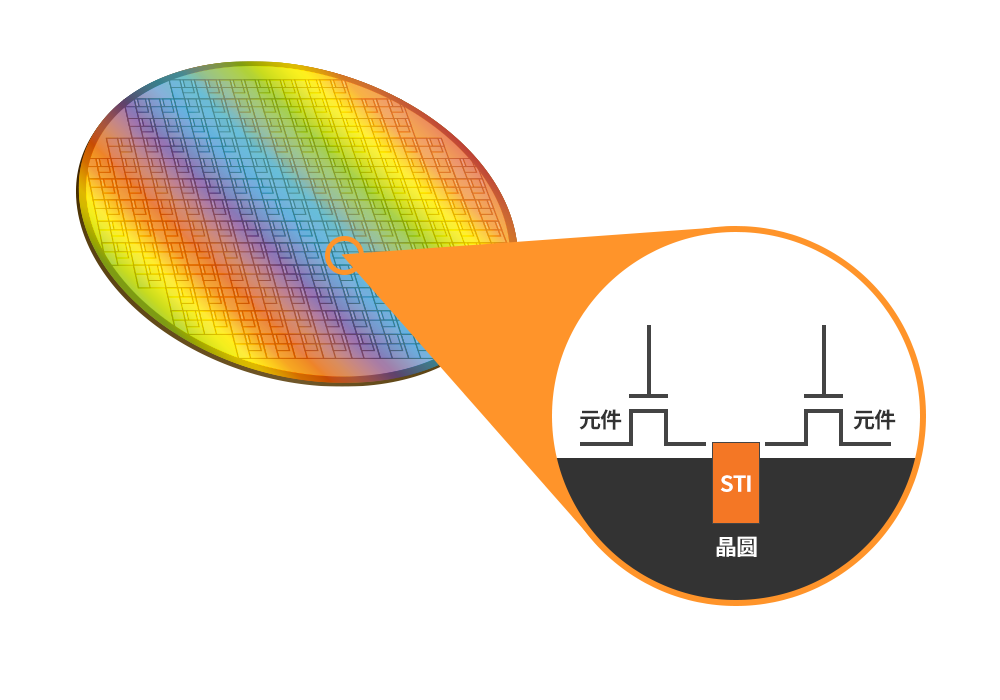

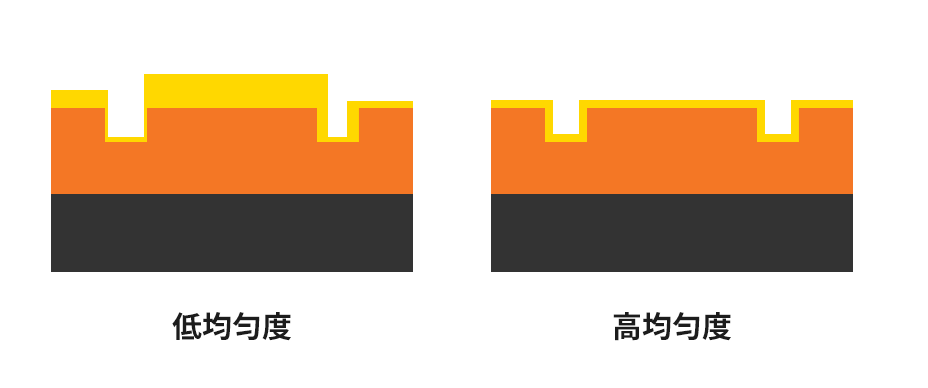

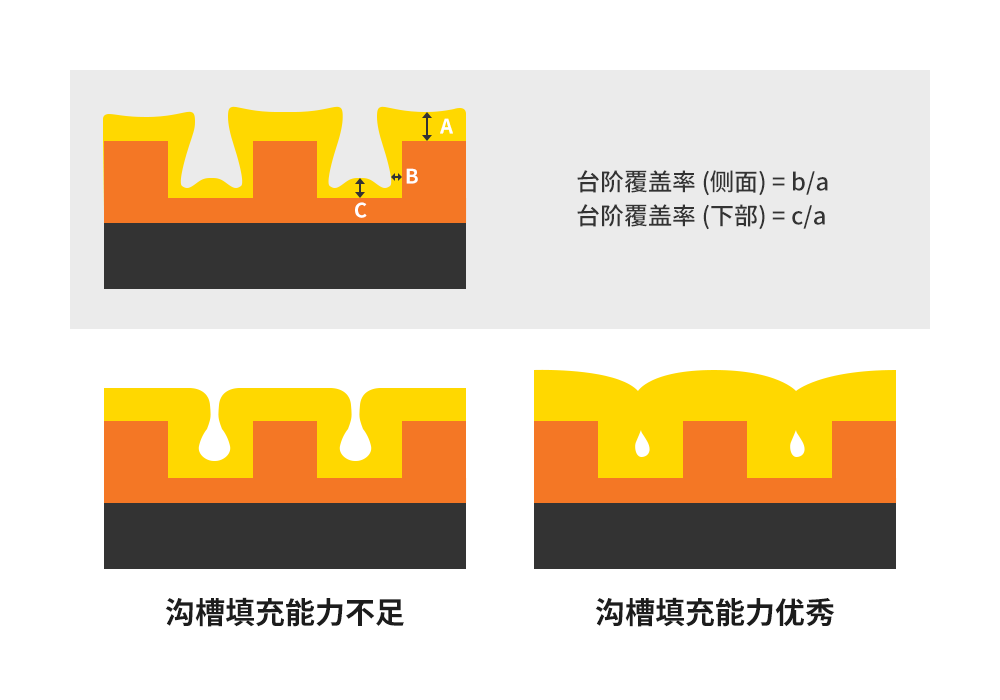

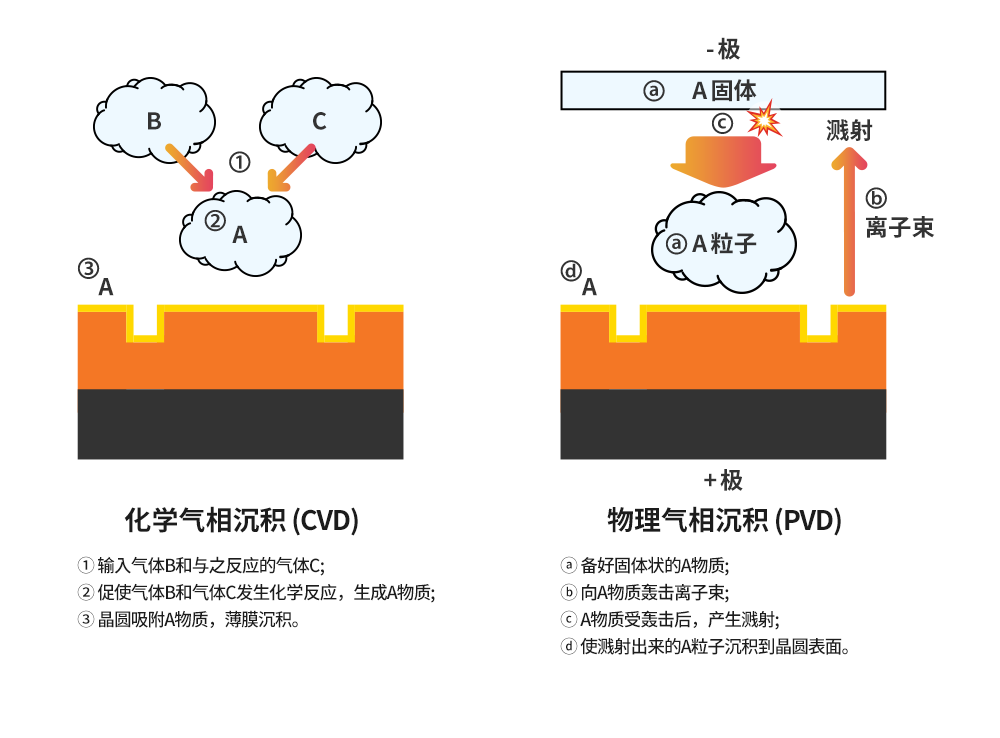

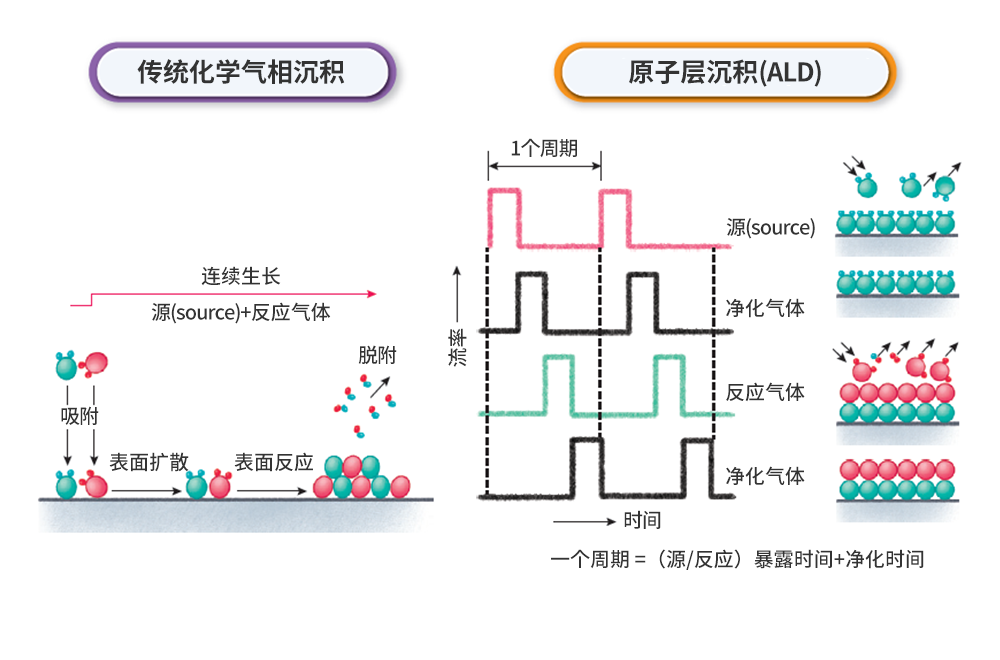

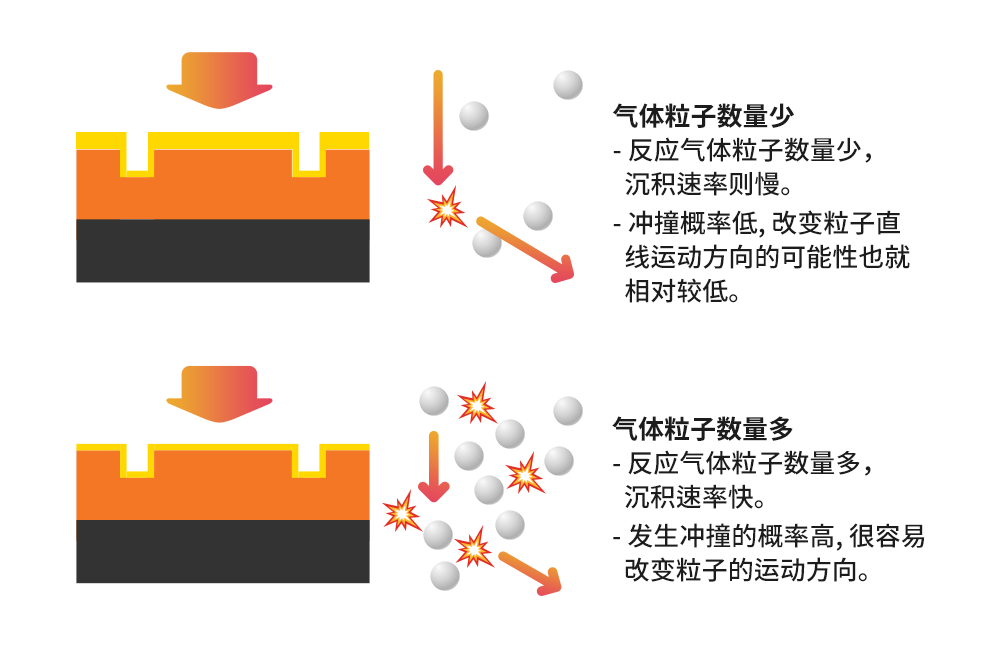

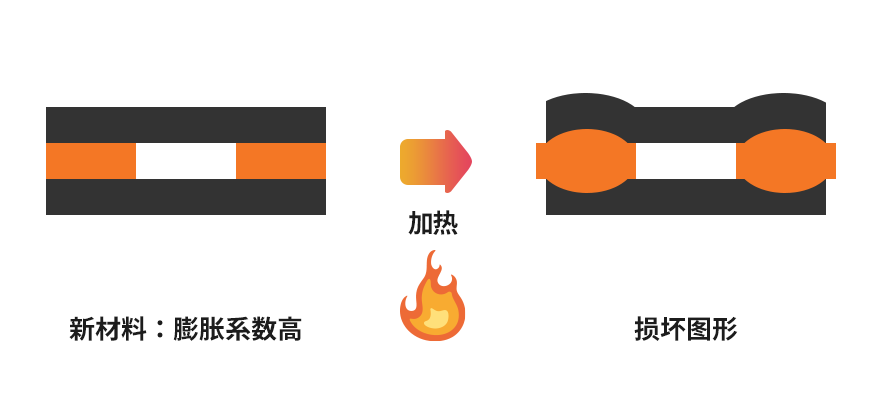

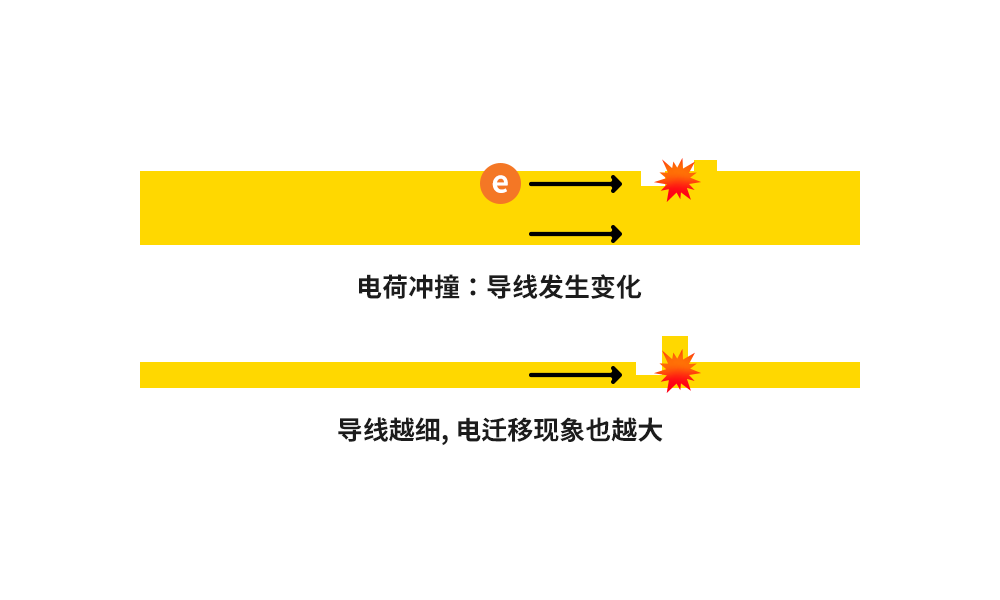

▲ 图1: 倒入巧克力糖浆后,再盖上一层饼干层 沉积工艺非常直观:将晶圆基底投入沉积设备中,待形成充分的薄膜后,清理残余的部分即可以进入下一道工艺了。 在半导体制程中,移除残余材料的“减法工艺”不止“刻蚀”一种,引入其他材料的“加法工艺”也非“沉积”一种。比如,光刻工艺中的光刻胶涂敷,其实也是在基底上形成各种薄膜;又如氧化工艺中晶圆(硅)氧化,也需要在基底表面添加各种新材料。那为什么唯独要强调“沉积”工艺呢? 这背后的原因,正是半导体的微细化趋势。如今,市场对电子产品的性能和低电耗的要求越来越高,这就需要更加“微细”的半导体来做支撑。如果采用体积更小、耗能更低的半导体,就可以在电子产品中添加更多功能。想实现半导体的微细化,就需要由不同材料沉积而成的薄膜层,使芯片内部不同部分各司其职。金属层就是其中的一种。过去,半导体制造商曾采用导电性*较高的铝做芯片的金属布线。但随着铝微细化技术遇到瓶颈,制造商就利用导电性更高的铜代替铝布线。但采用铜就出现了一个新问题,与铝不同,铜会扩散到不应扩散的地方(二氧化硅,SiO2)。为防止铜扩散,制造商们就必须在铜布线区形成阻挡层,即一种高质量的薄膜涂层。 半导体核心元件层与布线层厚度只有头发的数千分之一,想堆叠如此微细的元件和布线层,就需要沉积超薄且厚度极均匀的薄膜。这也是为什么沉积技术在半导体制程技术如此重要。本期文章所涉及的“沉积工艺”,又称为薄膜(Thin film)工艺,希望能为读者提供参考。 *导电性:物体传导电流的能力;金属等材料的导电性较高。 薄膜的分类与作用 “加法工艺”在半导体制程中至关重要,因为半导体是无法仅凭硅一种材料完成任何操作的:薄膜可以划分两个区域,使其不互相干扰;或通过互连电线,连接两个区域;必要时,还需要通过特殊的薄膜涂层来加强或减弱电场的力度;还可提前生成薄膜,为下一道工艺做准备等。接下来我们将详细讲解一下薄膜的几种作用。 介质薄膜是重要的半导体薄膜之一。它可用作电路间的绝缘层,掩蔽半导体核心元件的相互扩散和漏电现象,从而进一步改善半导体操作性能的可靠性;它还可用作保护膜,在半导体制程的最后环节生成保护膜,保护芯片不受外部冲击;或用作隔离膜,在堆叠一层层元件后进行刻蚀时,防止无需移除的部分被刻蚀。浅槽隔离(STI,Shallow Trench Isolation)*和金属层间电介质层(IMD,Intermetal Dieletric)*就是典型的例子。沉积材料主要有二氧化硅(SiO2),碳化硅(SiC)和氮化硅(SiN)等。 ▲ 图2: STI在相邻元件之间形成陡峭沟渠,防止漏电 另外,还有金属薄膜。芯片底部的元件(晶体管)如果未经连接是起不到任何作用的。想要使不同的元件各司其职,必须将它们与其他元件和电源连接起来。元件的连接需要通过钛、铜或铝等金属进行布线,连接金属布线和元件,还需要生成接触点(Contact)。这就像家电产品中连接电子线路板上的元件与元件时需焊接电线一样:连在电子线路板上的电线相当于半导体的金属布线,焊接点就相当于半导体内的接触点。 除此之外,沉积工艺在晶体管的高介电性薄膜和用于多重曝光*的硬掩模等方面应用范围也非常广泛。可以说,沉积在制造工艺中无处不在。不仅如此,过去没有采用沉积方式的工艺如今也开始采用沉积方式。高介电性薄膜就是其中之一。随着半导体的微细化发展,半导体需要更高质量、更精准的薄膜。因此,过去以氧化工艺制作的高介电性薄膜,如今也开始以沉积方式制作。 *浅槽隔离(STI,Shallow Trench Isolation):在相邻的元件之间形成陡峭的沟渠,在沟渠中填入氧化物形成元件隔离结构,以防止漏电。 *金属层间电介质层(IMD,Intermetal Dieletric):阻止金属布线层之间不必要电流的流动的保护膜。 * 多重曝光(Multi Patterning):通过重复的曝光和刻蚀工艺,追求更高图形密度和更小工艺节点的技术。 衡量沉积质量的主要指标: 均匀度、台阶覆盖率、沟槽填充 ▲ 图3:高均匀度&低均匀度的示例 在讲解薄膜沉积方式之前,我们先来了解几个衡量沉积质量的主要指标。这些指标与刻蚀工艺有很多相似之处。第一个指标就是均匀度。顾名思义,该指标就是衡量沉积薄膜厚度均匀与否的参数。薄膜沉积和刻蚀工艺一样,需将整张晶圆放入沉积设备中。因此,晶圆表面不同角落的沉积涂层有可能厚度不一。高均匀度表明晶圆各区域形成的薄膜厚度非常均匀。 第二个指标为台阶覆盖率(Step Coverage)。如果晶圆表面有断层或凹凸不平的地方,就不可能形成厚度均匀的薄膜。台阶覆盖率是考量膜层跨台阶时,在台阶处厚度损失的一个指标,即跨台阶处的膜层厚度与平坦处膜层厚度的比值。台阶覆盖率越接近1,表明跨台阶处(底部或侧壁)膜层厚度与平坦处膜层相差越少,越远离1(即越小于1)表明跨台阶处的膜层厚度对比平坦处膜层厚度越薄。 ▲ 图4:台阶覆盖率(上图)& 沟槽填充(下图)示例 最后一个指标是沟槽填充(Gap fill)。沟槽填充是衡量沟槽(Gap)填充程度的一个参数。如图4所示,半导体表面有很多凹凸不平的沟槽,沉积过程中很难保证可以把所有沟槽都填得严严实实。沟槽填充能力差,就会形成孔洞(Void),会影响材料的致密性,从而影响薄膜强度,造成坍塌。如果说“等向性刻蚀”是没有方向选择性地移除了不该移除的部分,沉积工艺中的“沟槽填充能力差”即表明没有填充到该填充的地方。 沉积方式 与前面我们所讲的工艺相同,沉积工艺也可分为化学气相沉积(CVD,Chemical Vapor Deposition)和物理气相沉积(PVD, Physical Vapor Deposition)。CVD是指通过化学方法在晶圆表面沉积涂层的方法,一般是通过给混合气体施加能量来进行。假设想在晶圆表面沉积物质(A),则需先向沉积设备输入可生成物质(A)的两种气体(B和C),然后给气体施加能量,促使气体B和C发生化学反应。 化学方程式如下: B + C + (能量等) → A + 副产物 CVD的优点是速率快,且由于在晶圆表面发生化学反应,拥有优秀的台阶覆盖率。但从上述化学方程式中不难看出,其缺点就是产生副产物废气。在半导体制程中,很难将这些废气完全排出,难免会参杂些不纯物质。因此,CVD多用于不需要精准把控材料特性的沉积涂层,如沉积各种消耗性的膜层(硬掩模)或各种厚绝缘薄膜等。 ▲ 图5:化学气相沉积 vs 物理气相沉积 PVD则向晶圆表面直接轰击要沉积的材料。也就是说,如果想在晶圆表面沉积A物质,则需将A物质气化后,使其沉积到晶圆表面。常用的PVD方法有溅射(Sputtering)*,这在刻蚀工艺中也曾涉及过。在这种方法中,我们先向A物质靶材(Target)轰击离子束(主要采用惰性气体),使A物质粒子溅射出来,再将脱落的粒子转移至硅片表面,并形成薄膜。 PVD的优点是无副产物,沉积薄膜的纯度高,且还可以沉积钨(W)、钴(Co)等无反应能力的纯净物材料。因此,多用于纯净物的金属布线。 还有一种比较特殊的方法,即原子层沉积(ALD,Atomic Layer Deposition)。前面说到的CVD和PVD两种方式,要么是通过气体的化学反应在晶圆表面沉积所需物质,要么是通过轰击离子束的物理过程沉积所需物质。ALD则与上述两种方式有所不同。如果想用这种方法在晶圆表面上沉积薄薄的一层A物质,则要先备好经反应后可生成A物质的反应物B和C。反应物B必须是容易被晶圆表面吸附的气体(前驱体,Precursor),反应物C则应具有较强的反应活性。在ALD过程中,需先把气体B吸附到晶圆表面,如果气体B之间很难相互吸附,晶圆表面将形成一层由气体B组成的原子层。然后,除去剩余气体B并输入气体C,使吸附在晶圆表面上的气体B和气体C发生反应,形成A物质和其他副产物气体,再除去多余的气体A和副产物气体。不断反复上述过程,以单原子膜形式一层一层地在基底表面镀膜。 ▲ 图6:传统CVD vs ALD (摘自:(株)图书出版HANOL出版社[半导体制造技术的理解293p]) ALD的最大优势在于沉积层极均匀的厚度与优异的台阶覆盖率。气态前驱体可纵横吸附,且ALD一个周期只沉积一层原子层。但正是因为单原子层需要逐次沉积,沉积速率也就慢了下来。因此,ADL多用于DRAM电容器等纵横比*高,需要高质量膜层的区域。 从上述对沉积工艺的说明中不难看出,沉积工艺中也存在需权衡之处:要提高均匀度等精确度,只能牺牲沉积速率。在整个半导体制程中,精确度和速率似乎永远位于跷跷板的两端,需要不断权衡。这对于沉积工艺来说也不例外。 *溅射(Sputtering):利用高能量轰击靶材,使其粒子离开其表面的物理过程。 *纵横比:高度与宽度的比值,纵横比高表示结构物的宽度相对较窄,高度却相对较高。 压力与温度 和在刻蚀工艺中一样,半导体制造商在沉积过程中也会通过控制温度、压力等不同条件来把控膜层沉积的质量。例如,降低压强,沉积速率就会放慢,但可以提高垂直方向的沉积质量。因为,压强低表明设备内反应气体粒子的数量少,粒子之间发生冲撞的概率就少,不会妨碍粒子的直线运动。施加高温则可以提高膜层的纯度。当然,这样一来就无法使用铝(其熔点为550度)等熔点低的金属材料。 ▲ 图7:压强对沉积工艺的影响 因此,在不同需求下,沉积相同材料也可采用完全不同的沉积方式。例如,同样是沉积二氧化硅(SiO2),栅极绝缘层与STI所需特性就不同,其沉积的方式也不同。栅极绝缘层是核心元件区域,要求较高的沉积质量,应采用高温低压的方式;STI则不然,它只要起到两个元件间的绝缘作用即可,通过低温高压的方式加快沉积速率才是关键。 材料选择上的难题 您或许常会在新闻中看到这样的报道:“发现了性能高出XX倍的新材料”。只看新闻内容,会感觉一场翻天覆地的半导体革命似乎即将来临。但在所谓的“新材料”中,真的能派上用场的却寥寥无几。因为,材料本身的特性好,并不代表它一定能制成高性能的半导体。对沉积材料的要求可不比沉积设备低。下面,我们来看一看材料的特性会对半导体制程产生什么样的影响。 ▲ 图8:加热导致图形损坏 物体遇热体积会变大,这种现象被称作热膨胀。铁轨之间留有缝隙就是为了防止铁轨在炎热的夏天因膨胀变形。半导体制程中也会出现这种热膨胀现象。问题在于,每一种材料的热膨胀程度不同,例如铝的热膨胀系数是氧化硅的40倍之多。举个比较极端的例子:如果在氧化硅上沉积了铝薄膜,即便铝薄膜沉积很成功,一旦进入后续的高温工艺,其内部结构就会完全被破损。换句话说,如果采用膨胀系数完全不同的材料替代之前的沉积材料,会严重影响高温条件下的产品良率。 ▲ 图9:电迁移现象 除此之外,还要考虑材料的电迁移(EM,Electromigration)现象。电迁移是指在金属布线上施加电流时,移动的电荷撞击金属原子,使其发生迁移的现象。铝等轻金属很容易发生这种电迁移现象。为防止铝的电迁移现象,半导体制造商们开始用铜布线替代铝,结果是又多了一道防止铜扩散的阻挡层沉积工艺。随着半导体不断微细化发展,铜布线也开始出现电迁移现象。为攻克这一难关,英特尔又用钴布线取代了铜。而既然核心金属布线层的材料发生了变化,上下层的工艺也肯定要跟着变。可见,想解决材料的电迁移现象,前后方的工艺也要随之发生很大变化。 要始终铭记:半导体制程是数百个工艺错综复杂紧密连接而成的,牵一发而动全身。新材料是好是坏,不能单看材料本身的特性,还要看能不能与前后方工艺相连,毕竟沉积材料不能独立存在。 结论:一种材料,多种方法 读到这儿,估计读者们已经发现了几点有趣之处了:首先,同样的材料可以通过不同的方法制成。例如,二氧化硅(SiO2)可以通过氧化工艺,也可以通过沉积工艺形成。即便是相同的材料,如果通过不同工艺涂敷到半导体上,其物理特性也会截然不同。 其次,氧化、刻蚀、沉积等看似完全不同的工艺其实有很多共同之处。比如,物理刻蚀中采用的溅射方法,在沉积工艺中同样也会使用,区别在于“是溅射要刻蚀的晶圆本身”,还是“把溅射出来的粒子沉积到晶圆上”。化学刻蚀中最重要的一点就是刻蚀气体与反应源生成的废气是否易于排放,化学气相沉积也同样如此。CVD过程中生成的副产物也要易于挥发、易于排放,这样后续工艺才会变得更容易。 可见,受半导体制造商青睐的新材料,并不是其本身特性有多优秀的材料,而是其沉积速率、纯度等特性易于控制的材料。而且,沉积材料还要易于通过刻蚀或CMP*等工艺去除。如果采用需要过高温度的材料,可能会因高温改变已沉积的其他材料。而若采用对温度非常敏感的材料,又会出现在下一道工艺中无法加热的问题。 如上文所述,“半导体制程由数百个制造工艺紧密连接而成”。想做好每一道工艺,对其他相关部门的业务也要有很好的把握。要擅于与同事沟通,更要懂得准确无误地传达自己的想法。一个半导体产品需要多人合作才可以完成,虽然过程有些辛苦,但也很值得。